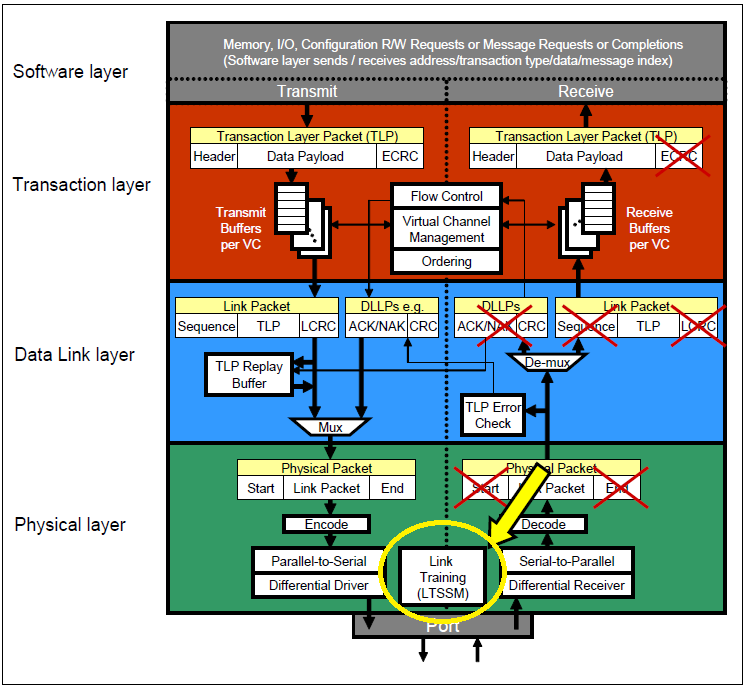

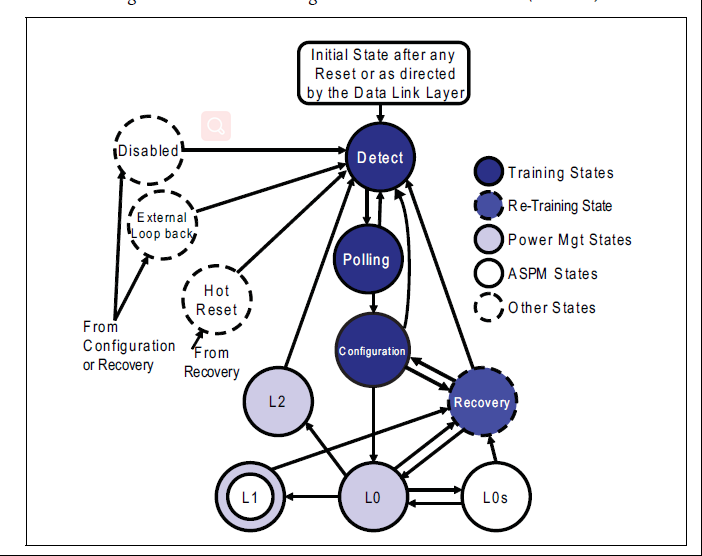

PCIe的链路训练指的是通过初始化PCIe连读的物理层、端口配置信息、发送接收模块以及相关的链路的状态,并了解链路对端的拓扑结构,最终让PCIe链路两端的设备进行数据通信的过程。PCIe spec上说链路训练的过程完全由硬件逻辑完成,无需系统软件的参与,但是事实上不同芯片厂商实现上还是有点区别,比如Intel和AMD的PCIe控制器都有一个专门的寄存器用来使能链路训练。链路训练的硬件逻辑实现在物理层,整个过程由链路训练状态机(Link Training and Status State Machine)完成,不需要其它层的参与。LTSSM在PCIe总线中的位置如下图所示:

链路训练主要目标

链路训练主要要达成位锁定(Bit Lock)、字符锁定(Symbol Lock)、块锁定(Block Lock)、确定链路宽度(Link Width)、通道位置翻转(Lane Reversal)、信号极性翻转(Polarity Inversion)、确定链路的数据率(Data Rate)和通道对齐(Lane-to-Lane De-skew)等功能。这些目标会在LTSSM进行链路训练时在某个步骤时完成。

-

位锁定:因为PCIe总线在进行数据传递时需要使用时钟进行同步,但是PCIe链路中并没有提供这个时钟信号,因此进行链路训练时接收端需要从发送端的数据报文中提取接收时钟,这个过程被称为位锁定。

-

字符锁定:在链路训练过程中,PCIe链路要首先确定COM字符,它标志着链路训练开始或者重新训练的开始,确定COM字符的标志被称为字符锁定。

-

链路宽度:一条PCIe总线提供的链路带宽可以是x1,x2,x4,x8等等,但是这个总线上的所挂接的设备并不完全使用这些链路。如一个x4的设备可能会接到x8的链路上,这时在链路训练时就必须通知对方实际的链路状态。

-

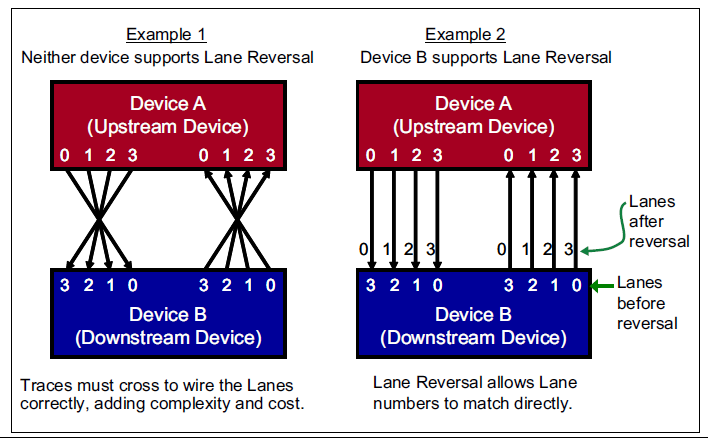

通道翻转:PCIe链路两端的设备所使用的的Lane可以错序进行连接,这个就是通道翻转。

-

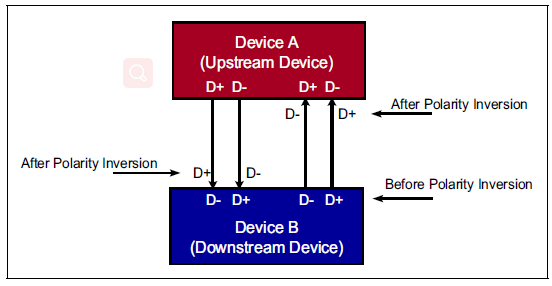

信号翻转:在相同的通道上,差分信号的极性也可以错序连接,这个就是信号翻转。

-

链路数据率:最初链路的训练和初始化都是基于2.5G T/S 也就是GEN1的速度的,如果链路两端都支持更高的速度则会自动retrain到更高的速度。

-

通道对齐:链路上的通道可能会不是同时到达的,有的可能早到有的可能晚到,链路就需要进行调整和补偿,这个就叫做通道对齐。

链路训练使用的字符序列

PCIe进行链路训练时要发送一些特殊的字符序列,这些序列也被称为PLP,物理层报文。这些字符序列主要有:

-

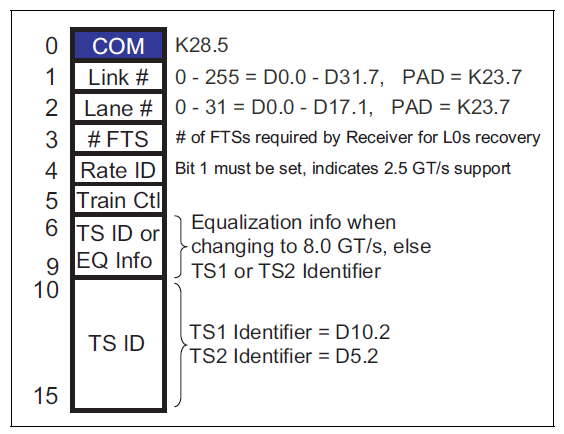

TS1 TS2序列。TS1(training sequence 1)主要用于检测PCIe链路的配置信息,TS2用来确认TS1的检测结果。TS序列gen1、gen2和gen3的格式有所不同,为了简化说明,我们以gen1、gen2格式来描述。 它们由16个symbol组成。第0个字符为COM控制字符表示序列的开始。第个字符在链路初始阶段为PAD(空字符),在配置阶段为该端口使用的Link number。第二个字符在初始阶段为PAD,在配置阶段为Lane number。第三个字符为FTS序列的个数。第四个字符为当前PCIe设备支持的数据传输速率。第五个字符存放命令。Bit0 hot reset,Bit1 Disable Link, Bit2 loopback, Bit3 Disable Scrambling, Bit4 Compliance Receive。接收端收到序列以后会根据该字符的命令进行对应的操作。 PCI spec 2.3在Command Register中引入了一个新的Interrupt Disable bit用来控制中断的enable和disable,该bit只会控制INTx类型的中断,不会影响MSIx。另外在Configuration Status Register加了一个Interrupt Status bit用来反应中断的状。

-

Idle 序列,当发送端进入Electrical Idle之前要向对端发送EIOS序列。出于Idle状态时PCIe链路使用的功耗最低。

-

FTS(Fast training sequence)序列由1个COM字符加上3个FTS字符组成,主要目的是使接收逻辑重新获得Bit/Symbol lock。

-

SKIP序列有1个COM加上3个SKP字符组成。主要用于时钟补偿。

链路训练状态机(LTSSM)

PCIe总线进行链路训练时会使用LTSSM,LTSSM状态机主要由11个状态组成Detect Polling Configuration Recovery L0 L0s L1 L2 Hot Reset Loopback和Disable状态。系统复位会自动进入Detect状态。

继续细分,这11个状态可以落到下述5个大类(如上图所示)。

-

链路训练 (Training States)

-

重训练(Re-Training State)

-

软件驱动功耗管理(Power Mgt States)

-

活动状态功耗管理(ASPM States)

-

其他(Other States)

其中1和2和链路训练相关,我们会详细介绍,其它的部分会在另外的文章中介绍。

-

链路训练状态:

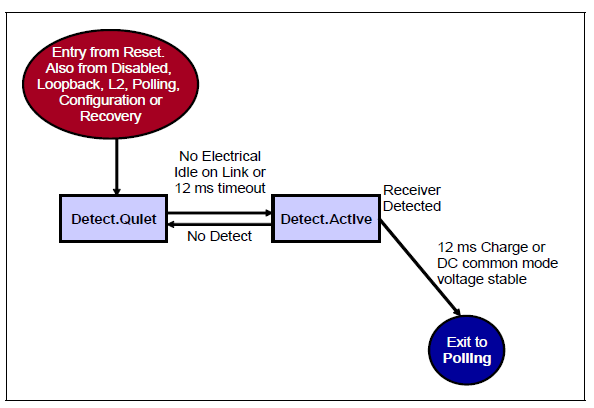

Detect状态:当PCIe链路被复位或者数据链路层通过寄存器操作会是的LTSSM进入该状态,该状态主要是发送端逻辑通过Receiver Detect判断接收端是否存在,如果存在就进入到Polling状态的过程。

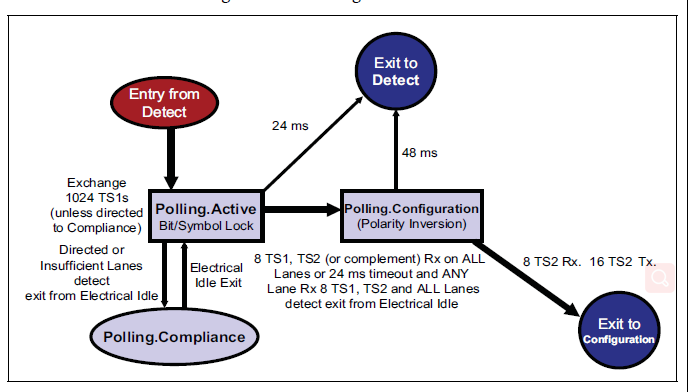

Polling状态:当链路进入该状态以后,将会向对方发送TS1和TS2序列,并接收对方发来的TS1和TS2序列,已达成Bit Lock, Symbol Lock和Lane的极性等我们之前已经介绍过的目标。

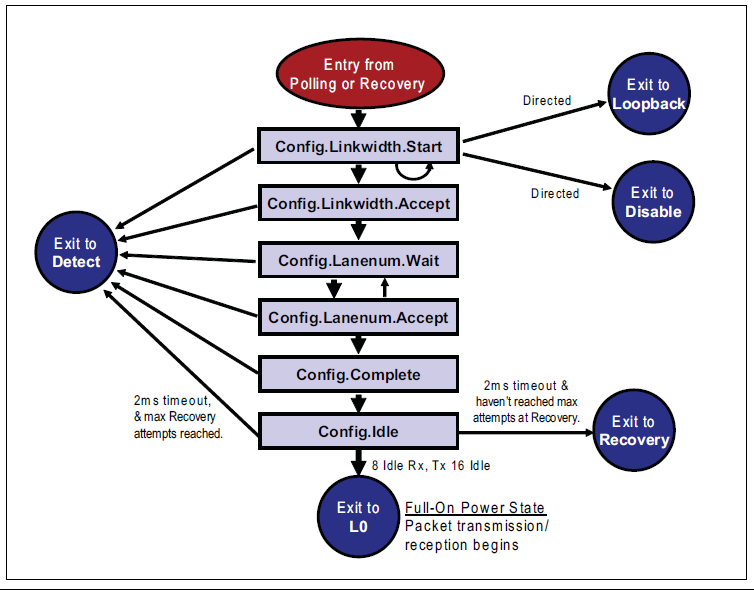

Configuration状态:该状态是LTSSM的重要状态,链路训练的几个主要的目标都在这个阶段完成包括链路的宽度,链路编号, 链路翻转, 极性翻转和通道对齐。

L0状态:它表示PCIe的链路进入正常工作状态,在这个状态下,PCIe链路可以正常的收发TLP、DLLP、PLP。

-

重训练状态:

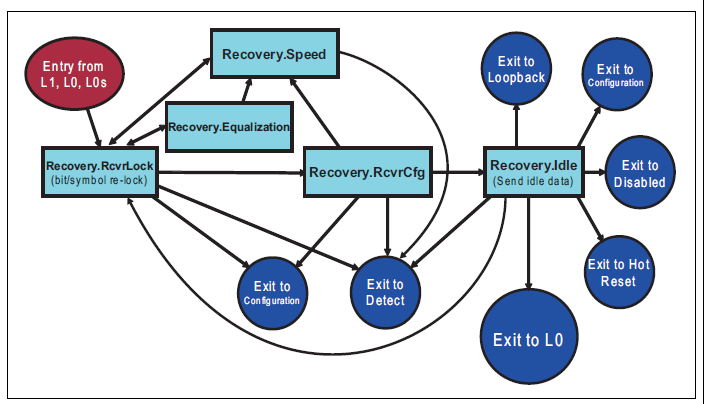

Recovery状态:当链路需要重新训练时需要进入该状态,通常是当改变数据传输速度或者是链路宽度以及从低功耗状态中回复的时候都需要进入该状态。在该状态中位锁定,符号锁定操作都会被重新进行。

Refer:

-

《PCI Express Technology》

-

《PCI Express 体系结构导读》